日期:2026-01-06

1月6日消息,在2025年国际电子器件会议(IEDM)上,英特尔首次公开展示了基于300mm硅基氮化镓(GaN)工艺的Chiplet技术。此项突破性技术有望革新高性能功率电子和射频器件的未来,特别是在5G/6G通信、人工智能服务器和高效能计算领域的应用。

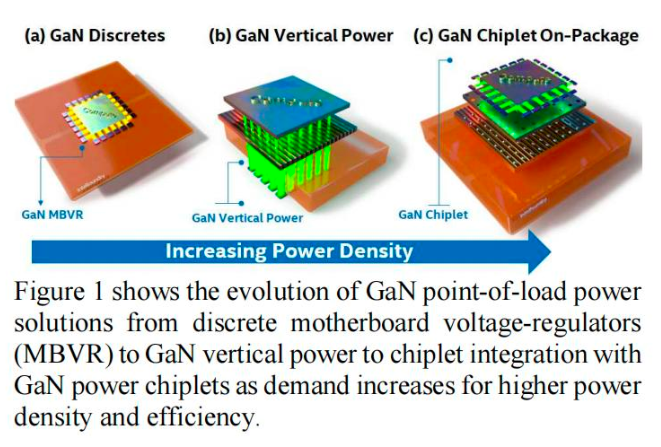

英特尔展示的氮化镓Chiplet采用了业界最薄的19µm硅衬底,并成功集成了GaN N-MOSHEMT与硅PMOS的单片CMOS数字电路库。这一创新标志着氮化镓技术从分立器件迈向系统级集成,推动了氮化镓在功率密度和效率要求日益提高的电子设备中的应用。

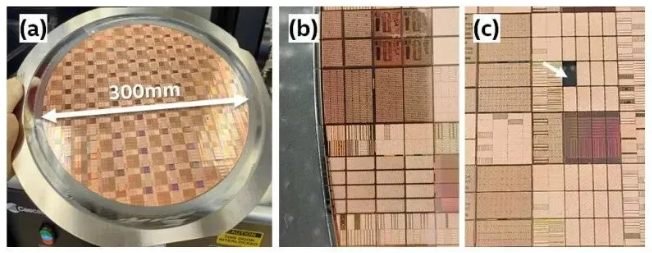

与传统的150mm硅晶圆相比,300mm硅基氮化镓晶圆的应用能够显著降低生产成本并提高生产效率。该技术平台兼容现有的CMOS工艺线,为氮化镓的广泛商业化应用铺平了道路。

该氮化镓Chiplet的硅衬底经过完全加工、减薄和单晶化,厚度仅为19µm,较传统方案减少了60%以上。这一超薄设计有助于更高效的三维集成,为功率密度和散热性能提供了理想基础。通过采用SDBG技术,晶圆在减薄和切割过程中能够保持结构完整性,表面粗糙度控制在纳米级别,确保了混合键合的高效进行。

此外,减薄设计大幅降低了硅通孔(TSV)的深宽比,减少了电阻损耗约40%,同时热阻也下降了35%,大大提升了功率密度和散热能力。

英特尔的氮化镓Chiplet在电气性能上表现卓越。30nm栅长的GaN MOSHEMT晶体管,导通电阻(RON)低于5mΩ·mm²,栅极和漏极漏电流低于3pA/µm,功耗控制优秀。击穿电压(BVDS)达到78V@1µA/µm,满足中压应用需求。在射频性能方面,30nm晶体管的截止频率(fT)为212GHz,最大振荡频率(fMAX)达到304GHz,适合毫米波通信等高频应用。

该Chiplet的电流密度接近10A/mm²,预计通过进一步缩小几何尺寸,电流密度将进一步提升,推动高功率应用的实现。

单片集成CMOS数字电路库

最具创新性的突破之一是该技术实现了GaN N-MOSHEMT与硅PMOS的单片集成,成功在300mm硅基氮化镓晶圆上构建了完整的CMOS数字电路库。通过统一的工艺设计套件(PDK),英特尔实现了反相器、逻辑门、多路复用器、触发器和环形振荡器等基本数字电路的集成。

这一集成能力显著减少了对外部硅芯片的依赖,提升了系统的响应速度和可靠性。

英特尔对该技术进行了严格的可靠性验证,结果显示其在高温、时间相关介质击穿(TDDB)和热载流子注入(HCI)测试中的表现均符合工业级标准。尤其是,在90°C下,栅极氧化层的预计寿命超过10年,保证了长期稳定运行。

展望未来,英特尔计划在2026-2027年间实现该技术的小批量量产。初期应用将集中于数据中心的电源管理、5G基站功放模块和新能源汽车的充电系统等领域。随着技术的不断成熟,预计氮化镓Chiplet将在高效能计算、绿色能源和高速通信等领域发挥关键作用。

尽管技术前景广阔,产业化仍面临一些挑战。例如,19µm超薄晶圆的处理和加工需要专用设备,设备投资成本较高。此外,GaN与硅的热膨胀系数差异可能导致热循环可靠性问题,需要开发新的界面材料。而CMOS与GaN工艺的协同优化复杂度高,也对设计自动化工具链提出了更高要求。

未来,英特尔计划继续推进技术的经济性提升,扩展到8英寸晶圆,并开发适用于600V以上的高压器件,以拓展更广泛的工业应用。预计到2028年,硅基氮化镓市场规模将达到50亿美元,年复合增长率超过30%。